Abstract

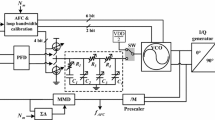

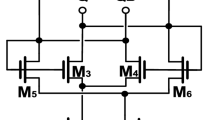

A 0.20–2.43 GHz fractional-N frequency synthesizer is presented for multi-band wireless communication systems, in which the scheme adopts low phase noise voltage-controlled oscillators (VCOs) and a charge pump (CP) with reduced current mismatch. VCOs that determine the out-band phase noise of a phase-locked loop (PLL) based frequency synthesizer are optimized using an automatic amplitude control technique and a high-quality factor figure-8-shaped inductor. A CP with a mismatch suppression architecture is proposed to improve the current match of the CP and reduce the PLL phase errors. Theoretical analysis is presented to investigate the influence of the current mismatch on the output performance of PLLs. Fabricated in a TSMC 0.18-µm CMOS process, the prototype operates from 0.20 to 2.43 GHz. The PLL synthesizer achieves an in-band phase noise of −96.8 dBc/Hz and an out-band phase noise of −122.8 dBc/Hz at the 2.43-GHz carrier. The root-mean-square jitter is 1.2 ps under the worst case, and the measured reference spurs are less than −65.3 dBc. The current consumption is 15.2 mA and the die occupies 850 µm×920µm.

摘要

提出一种适用于多标准无线通信系统的0.20–2.43 GHz分数分频频率合成器方案, 该方案采用低相位噪声压控振荡器和低电流失配电荷泵. 由于压控振荡器的性能决定了锁相环型频率合成器的带外相位噪声, 利用自动幅度控制技术和高品质因数的8字型电感对压控振荡器进行优化. 为改善电荷泵电流匹配性能以及减小锁相环相位误差, 提出一种具有失配抑制结构的电荷泵. 通过理论分析, 研究了电流失配对锁相环输出性能的影响. 采用台积电0.18-µm CMOS工艺, 模型输出频率从0.20 GHz变化到2.43 GHz. 这一锁相环型频率合成器在2.43 GHz载波时实现的带内相位噪声为−96.8 dBc/Hz, 带外相位噪声为−122.8 dBc/Hz. 在最坏情况下, 均方根抖动为1.2 ps, 测量的参考杂散小于−65.3 dBc. 消耗电流15.2 mA, 芯片面积为850 µm×920 µm.

Similar content being viewed by others

References

Berny AD, Niknejad AM, Meyer RG, 2005. A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration. IEEE J Sol-State Circ, 40(4):909–917. https://doi.org/10.1109/JSSC.2004.842851

Chang HH, Wang PY, Zhan JHC, et al., 2008. A fractional spur-free ADPLL with loop-gain calibration and phase-noise cancellation for GSM/GPRS/EDGE. IEEE Int Conf on Solid-State Circuits, p.200–201, 606. https://doi.org/10.1109/ISSCC.2008.4523126

Chang WS, Huang PC, Lee TC, 2014. A fractional-N divider-less phase-locked loop with a subsampling phase detector. IEEE J Sol-State Circ, 49(12):2964–2975. https://doi.org/10.1109/JSSC.2014.2359670

Chiu WH, Chang TS, Lin TH, 2009. A charge pump current missmatch calibration technique for ΔΣ fractional-N PLLs in 0.18-µm CMOS. IEEE Asian Solid-State Circuits Conf, p.73–76. https://doi.org/10.1109/ASSCC.2009.5357182

de Muer B, Steyaert MSJ, 2002. A CMOS monolithic ΔΣ-controlled fractional-N frequency synthesizer for DCS-1800. IEEE J Sol-State Circ, 37(7):835–844. https://doi.org/10.1109/JSSC.2002.1015680

Deng W, Musa A, Okada K, et al., 2012. A 0.38 mm2, 10 MHz-6.6 GHz quadrature frequency synthesizer using fractional-N injection-locked technique. IEEE Asian Solid State Circuits Conf, p.353–356. https://doi.org/10.1109/ASSCC.2012.6570787

Deng W, Hara S, Musa A, et al., 2014. A compact and low-power fractionally injection-locked quadrature frequency synthesizer using a self-synchronized gating injection technique for software-defined radios. IEEE J Sol-State Circ, 49(9):1984–1994. https://doi.org/10.1109/JSSC.2014.2334392

Gao X, Klumperink EAM, Socci G, et al., 2010. Spur reduction techniques for phase-locked loops exploiting a sub-sampling phase detector. IEEE J Sol-State Circ, 45(9):1809–1821. https://doi.org/10.1109/JSSC.2010.2053094

Hara S, Okada K, Matsuzawa A, 2010. 10 MHz to 7 GHz quadrature signal generation using a divide-by-4/3, -3/2, -5/3, -2, -5/2, -3, -4, and -5 injection-locked frequency divider. Symp on VLSI Circuits, p.51–52. https://doi.org/10.1109/VLSIC.2010.5560270

Hedayati H, Bakkaloglu B, Khalil W, 2009. A 1 MHz-bandwidth type-I ΔΣ fractional-N synthesizer for Wi-MAX applications. IEEE Int Conf on Solid-State Circuits, p.390–391, 391a. https://doi.org/10.1109/ISSCC.2009.4977472

Hsu CM, Straayer MZ, Perrott MH, 2008. A low-noise, wide-BW 3.6 GHz digital ΔΣ fractional-N frequency synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation. IEEE Int Conf on Solid-State Circuits, p.340–617. https://doi.org/10.1109/ISSCC.2008.4523196

Huh H, Koo Y, Lee KY, et al., 2005. Comparison frequency doubling and charge pump matching techniques for dualband ΔΣ fractional-N frequency synthesizer. IEEE J Sol-State Circ, 40(11):2228–2236. https://doi.org/10.1109/JSSC.2005.857368

Italia A, Ippolito CM, Palmisano G, 2012. A 1-mW 1.13–1.9 GHz CMOS LC VCO using shunt-connected switched-coupled inductors. IEEE Trans Circ Syst I, 59(6):1145–1155. https://doi.org/10.1109/TCSI.2011.2173383

Jeong CH, Kim KY, Kwon CK, et al., 2013. Digital calibration technique using a signed counter for charge pump mismatch in phase-locked loops. IET Circ Dev Syst, 7(6): 313–318. https://doi.org/10.1049/iet-cds.2013.0011

Liang CF, Chen SH, Liu SI, 2008. A digital calibration technique for charge pumps in phase-locked systems. IEEE J Sol-State Circ, 43(2):390–398. https://doi.org/10.1109/JSSC.2007.914283

Liao DY, Wang HC, Dai FF, et al., 2017. An 802.11a/b/g/n digital fractional-N PLL with automatic TDC linearity calibration for spur cancellation. IEEE J Sol-State Circ, 52(5):1210–1220. https://doi.org/10.1109/JSSC.2016.2638882

Lim CC, Ramiah H, Yin J, et al., 2016. A high-Q spiral inductor with dual-layer patterned floating shield in a class-B VCO achieving a 190.5-dBc/Hz FoM. IEEE Int Symp on Circuits and Systems, p.2759–2762. https://doi.org/10.1109/ISCAS.2016.7539164

Mahmoud A, Fanori L, Mattsson T, et al., 2016. A 2.8-to-5.8 GHz harmonic VCO based on an 8-shaped inductor in a 28 nm UTBB FD-SOI CMOS process. Analog Integr Circ Signal Process, 88(3):391–399. https://doi.org/10.1007/s10470-016-0759-4

Narayanan AT, Katsuragi M, Kimura K, et al., 2016. A fractional-N sub-sampling PLL using a pipelined phase-interpolator with an FoM of −250 dB. IEEE J Sol-State Circ, 51(7):1630–1640. https://doi.org/10.1109/JSSC.2016.2539344

Nuzzo P, Vengattaramane K, Ingels M, et al., 2009. A 0.1–5 GHz dual-VCO software-defined ΔΣ frequency synthesizer in 45 nm digital CMOS. Proc IEEE Radio Frequency Integrated Circuits Symp, p.321–324. https://doi.org/10.1109/RFIC.2009.5135549

Osmany SA, Herzel F, Scheytt JC, 2010. An integrated 0.6–4.6 GHz, 5–7 GHz, 10–14 GHz, and 20–28 GHz frequency synthesizer for software-defined radio applications. IEEE J Sol-State Circ, 45(9):1657–1668. https://doi.org/10.1109/JSSC.2010.2051476

Pamarti S, Jansson L, Galton I, 2004. A wideband 2.4-GHz delta-sigma fractional-NPLL with 1-Mb/s in-loop modulation. IEEE J Sol-State Circ, 39(1):49–62. https://doi.org/10.1109/JSSC.2003.820858

Ruippo P, Lehtonen TA, Tchamov NT, 2010. An UMTS and GSM low phase noise inductively tuned LC VCO. IEEE Microw Wirel Compon Lett, 20(3):163–165. https://doi.org/10.1109/LMWC.2010.2040219

Sharkia A, Mirabbasi S, Shekhar S, 2018. A 0.01 mm2 4.6-to-5.6GHz sub-sampling type-I frequency synthesizer with −254 dB FOM. Proc IEEE Int Conf on Solid-State Circuits, p.256–258. https://doi.org/10.1109/ISSCC.2018.8310281

Temporiti E, Albasini G, Bietti I, et al., 2004. A 700-kHz bandwidth ΣΔ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications. IEEE J Sol-State Circ, 39(9):1446–1454. https://doi.org/10.1109/JSSC.2004.831598

Wang KJ, Swaminathan A, Galton I, 2008. Spurious tone suppression techniques applied to a wide-bandwidth 2.4 GHz fractional-N PLL. IEEE J Sol-State Circ, 43(12): 2787–2797. https://doi.org/10.1109/JSSC.2008.2005716

Wu Y, Shahmohammadi M, Chen Y, et al., 2017. A 3.5–6.8-GHz wide-bandwidth DTC-assisted fractional-N all-digital PLL with a MASH ΣΔ-TDC for low in-band phase noise. IEEE J Sol-State Circ, 52(7):1885–1903. https://doi.org/10.1109/JSSC.2017.2682841

Yoon H, Lee Y, Kim JJ, et al., 2014. A wideband dual-mode LC-VCO with a switchable gate-biased active core. IEEE Trans Circ Syst II, 61(5):289–293. https://doi.org/10.1109/TCSII.2014.2305216

Yu SA, Baeyens Y, Weiner J, et al., 2011. A single-chip 125-MHz to 32-GHz signal source in 0.18-µm SiGe BiCMOS. IEEE J Sol-State Circ, 46(3):598–614. https://doi.org/10.1109/JSSC.2011.2104551

Yu YH, Chen JH, Chen YJE, 2018. A wideband 90-nm CMOS phase-locked loop with current mismatch calibration for spur reduction. IEEE Conf on Asia-Pacific Microwave, p.1504–1506. https://doi.org/10.23919/APMC.2018.8617454

Zhang Z, Zhu G, Yue CP, 2019. 30.8 A 0.65V 12-to-16GHz sub-sampling PLL with 56.4fsrms integrated jitter and −256.4dB FoM. IEEE Int Conf on Solid-State Circuits, p.488–490. https://doi.org/10.1109/ISSCC.2019.8662378

Author information

Authors and Affiliations

Contributions

Wei ZOU designed the research and drafted the manuscript. Daming REN processed the data and helped organize the manuscript. Wei ZOU and Xuecheng ZOU revised and finalized the paper.

Corresponding author

Ethics declarations

Wei ZOU, Daming REN, and Xuecheng ZOU declare that they have no conflict of interest.

Additional information

Project supported by the National Natural Science Foundation of China (No. 61376031)

Rights and permissions

About this article

Cite this article

Zou, W., Ren, D. & Zou, X. A 0.20–2.43 GHz fractional-N frequency synthesizer with optimized VCO and reduced current mismatch CP. Front Inform Technol Electron Eng 22, 251–261 (2021). https://doi.org/10.1631/FITEE.1900653

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/FITEE.1900653