Abstract

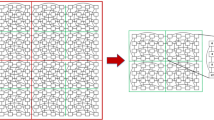

Interconnection networks play a major role in differentiating modern multiprocessor architectures. They can be categorized according to a number of criteria such as topology, routing strategy and switching technique. They are built up of switching elements; the topology is packaged such that it is cost effective along with its ability to achieve good performance. In this paper, we have studied an existing X-Torus topology (Gu et al. in ICCSA, LNCS, vol. 3984, pp. 149–157, 2006) which is an enhancement of a Torus network by adding Cross Links, and hence contributes to shorter diameter, shorter average distance and larger bisection bandwidth. Furthermore, we proposed the Adaptive Load Balanced Routing (ALBR) algorithm and Dual Adaptive Routing (DAR) algorithm.

The ALBR algorithm can manage traffic during congestion by sensing the same through Channel Queues. The strength of the Algorithm lies in the fact that using backtracking, the number of lookups to reach destination through Cross Link decreases, thereby making optimal use of them. The Performance aspects for both Odd and Even forms of X-Torus are tested on Network Simulator-2 (NS-2) using Perl and Gawk for analyzing text of trace files generated during simulation.

The DAR reduces the number of lookups by optimal utilization of Cross Links but also helps to curb the problem of packet congestion, which could be a major issue in X-Torus due to the presence of Cross Links. In order to improve its rooting performance we have provided a new approach to handle the problem of deadlock detection and recovery mechanism in the case of X-Torus. The proposed progressive deadlock recovery mechanism takes advantage of the high path diversity of X-Torus. We also present a low cost and simple mechanism for deadlock detection as against many conservative mechanisms.

Similar content being viewed by others

References

Siegel HJ, Stunkel CB (1996) Inside parallel computers: trends in interconnection networks. IEEE Comput Sci Eng 3(3):69–71. Invited

Gu H, Xie Q, Wang K, Zhang J, Li Y (2006) X-Torus: a variation of Torus topology with lower diameter and larger bisection width. In: ICCSA 2006. LNCS, vol 3984. Springer, Berlin, pp 149–157

Anderson Ed., Brooks J, Grassl C, Scott S (1997) Performance of the cray T3E multiprocessor. In: Supercomputing (97), San Jose, California, pp 1–17

Seitz CL (1988) The architecture and programming of the Ameteck series 2010 multicomputer. In: Proceedings of the 3rd conference on hypercube concurrent computers and applications, vol 1, pp 33–36

Lillevik L (1991) The touchstone 30 gigaflop DELTA prototype. In: Proceedings of the 6th distributed memory computing conference, pp 671–677

Dally WJ (2001) Scalable switching fabrics for Internet routers, White paper. Avici Systems Incorporation

Bhuyan LN (ed) (1987) Special issue of Interconnection networks. IEEE Comput 20(6). doi:10.1109/MC.1987.1663580

Siegel HJ (1990) Interconnection network for large scale parallel processing: theory and case studies. McGraw-Hill, New York. ISBN:0-07-057561-4

Hwang K (2000) Advanced computer architecture: parallelism, scalability, programmability. Tata McGraw-Hill, New Delhi. ISBN:0-07-053070-X

Duato J, Yalamanchili S, Ni LM (2003) Interconnection networks: an engineering approach. Morgan Kaufmann, San Francisco. ISBN:1-55860-852-4

Dally W, Towles B (2004) Principles and practices of interconnection networks. Morgan Kaufmann, San Francisco. ISBN:978-0-12-200751-4

Arabnia HR, Oliver MA (1987) Arbitrary rotation of raster images with SIMD machine architectures. Int J Eurograph Assoc (Comput Graph Forum) 6(1):3–12

Bhandarkar SM, Arabnia HR, Smith JW (1995) A reconfigurable architecture for image processing and computer vision. Int J Pattern Recogn Artif Intell 9(2):201–229 (special issue on VLSI algorithms and architectures for computer vision, image processing, pattern recognition and AI)

Bhandarkar SM, Arabnia HR (1995) The hough transform on a reconfigurable multi-ring network. J Parallel Distrib Comput 24(1):107–114

Wani MA, Arabnia HR (2003) Parallel edge-region-based segmentation algorithm targeted at reconfigurable multi-ring network. J Supercomput 25(1):43–63

Duato J (1993) A new theory of deadlock-free adaptive routing in wormhole networks. IEEE Trans Parallel Distrib Syst 4(12):1320–1331

Duato J (1995) A necessary and sufficient condition for dead lock-free adaptive routing in wormhole networks. IEEE Trans Parallel Distrib Syst 6(10):1055–1067

Dally WJ, Seitz CL (1987) Deadlock-free message routing in multiprocessor interconnection networks. IEEE Trans Comput C-36(5):547–553

Dally WJ, Aoki H (1993) Deadlock-free adaptive routing in multi computer networks using virtual channels. IEEE Trans Parallel Distrib Syst 4(4):466–475

Duato J (1993) Deadlock-free adaptive routing algorithms for the 3DTorus: limitations and solutions. In: Proceedings of parallel architectures and languages Europe 93

Nitin, Subramanian A (2008) Efficient algorithms to solve dynamic MINs stability problems using stable matching with complete TIES. J Discrete Algorithms 6(3):353–380

Singh A, Dally WJ, Gupta AK, Towels B (2004) Adaptive channel queue routing on k-ary n-cubes. In: Proceedings of the sixteenth annual ACM symposium on parallelism in algorithms and architectures

Nitin, Chauhan DS (2010) Stochastic communication for application specific Networks-on-Chip. J Supercomput. doi:10.1007/s11227-010-0472-5

Nitin, Garhwal S, Srivastava N (2009) Designing a fault-tolerant fully-chained combining switches multi-stage interconnection network with disjoint paths. J Supercomput. doi:10.1007/s11227-009-0336-z

Rakesh N, Nitin (2010) Analysis of multi-sort algorithm on multi-mesh of trees (MMT) architecture. J Supercomput. doi:10.1007/s11227-010-0404-4

Nitin, Chauhan DS (2010) Comparative analysis of traffic patterns on k-ary n-tree using adaptive algorithms based on Burton Normal Form. J Supercomput. doi:10.1007/s11227-010-0454-7

Nitin, Sehgal VK, Bansal PK (2007) On MTTF analysis of a fault-tolerant hybrid MINs. WSEAS Trans Comput Res 2(2):130–138. ISSN 1991-8755

Nitin (2006) Component level reliability analysis of fault-tolerant hybrid MINs. WSEAS Trans Comput 5(9):1851–1859. ISSN 1109-2750

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nitin, Vaish, R. & Shrivastava, U. On a deadlock and performance analysis of ALBR and DAR algorithm on X-Torus topology by optimal utilization of Cross Links and minimal lookups. J Supercomput 59, 1252–1288 (2012). https://doi.org/10.1007/s11227-010-0524-x

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-010-0524-x