Abstract

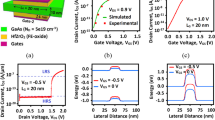

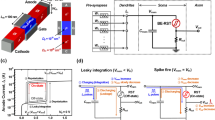

This work aims to present a novel energy-efficient single transistor leaky integrate-and-fire neuron for future neuromorphic computing. It comprises of a SiGe-based MOSFET, having channel length of 400 nm. Using 2D simulation, it has been verified that the proposed SiGe-based single transistor neuron accurately mimics the spiking behavior of the biological neuron, while eliminating the need of external circuitry and exorbitant energy consumption. The neuron consumes energy of 3.8 pJ/spike, which is 11.8 times and 2.1 times lesser than the previously proposed Si-based and Ge-based single transistor neurons, respectively. It also shows improvement in terms of controllability, simplicity, integration density, and fabrication process. By designing threshold logic gates, the proposed neuron has been employed to implement universal digital logic functions, such as NAND and NOR. Finally, the recognition ability for MNIST handwritten digits has been verified. It has been confirmed that besides imitating the neuronal behavior accurately, the proposed neuron can also be used in practical spiking neural networks for image classification with an accuracy of 93.79%.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Shafique K, Khawaja BA, Sabir F, Qazi S, Mustaqim M (2020) Internet of things (IoT) for next-generation smart systems: a review of current challenges, Future trends and prospects for emerging 5G-IoT scenarios. IEEE Access 8:23022–23040. https://doi.org/10.1109/ACCESS.2020.2970118

Zou X, Xu S, Chen X, Yan L, Han Y (2021) Breaking the von Neumann bottleneck: architecture-level processing-in-memory technology. Sci China Inf Sci. https://doi.org/10.1007/s11432-020-3227-1

Silver D, Huang A, Maddison CJ, Guez A, Sifre L, Driessche G, Schrittwieser J, Antonoglou I, Panneershelvam V, Lanctot M, Dieleman S, Grewe D, Nham J, Kalchbrenner N, Sutskever I, Lillicrap T, Leach M, Kavukcuoglu K, Graepel T, Hassabis D (2016) Mastering the game of go with deep neural networks and tree search. Nature 529:484–489. https://doi.org/10.1038/nature16961

Sugie T, Akamatsu T, Nishitsuji T, Hirayama R, Masuda N, Nakayama H, Ichihashi Y, Shiraki A, Oikawa M, Takada N, Endo Y, Kakue T, Shimobaba T (2018) Ito High-performance parallel computing for next-generation holographic imaging. Nat Electron 1:254–259. https://doi.org/10.1038/s41928-018-0057-5

Maass W (1997) Networks of spiking neurons: the third generation of neural network models. Neural Netw 10(9):1659–1671. https://doi.org/10.1016/S0893-6080(97)00011-7

Khanday FA, Dar MR, Kant NA, Rossello JL, Psychalinos C (2018) 065 V integrable electronic realisation of integer- and fractional-order Hindmarsh-Rose neuron model using companding technique. Special Issue Low Voltage Low Power Integr Circuits Syst IET Circuits Devices Syst 12(6):696–706. https://doi.org/10.1049/iet-cds.2018.5033

Shaban A, Bezugam SS, Suri M (2021) An adaptive threshold neuron for recurrent spiking neural networks with nanodevice hardware implementation. Nat Commun 12(1):4234. https://doi.org/10.1038/s41467-021-24427-8

Kant NA, Dar MR, Khanday FA, Psychalinos C (2017) Ultra-low-voltage integrable electronic realization of integer- and fractional-order Liao’s chaotic delayed neuron model. Circuits Syst Signal Process 36(12):4844–4868. https://doi.org/10.1007/s00034-017-0615-5

Liao X, Song W, Zhang X, Yan C, Li T, Ren H, Liu C, Wang Y, Zheng Y (2020) A bioinspired analogous nerve towards artificial intelligence. Nat Commun 11(1):268. https://doi.org/10.1038/s41467-019-14214-x

Khanday FA, Kant NA, Dar MR, Zulkifli TZA, Psychalinos C (2019) Low-voltage low-power integrable CMOS circuit implementation of integer- and fractional-order FitzHugh–Nagumo neuron model. IEEE Trans Neural Netw Learn Syst 30(7):2108–2122

Joubert A, Belhadj B, Temam O, Heliot R (2012) Hardware spiking neurons design: Analog or digital?. In: Proc. Int. Joint Conf. Neural Netw. (IJCNN), Brisbane, QLD, Australia, Jun. pp. 1–5. https://doi.org/10.1109/IJCNN.2012.6252600

Kant NA, Khanday FA, Psychalinos C (2014) 0.5V Sinh-Domain design of activation functions and neural networks. J Low Power Electron 10(2):201–213. https://doi.org/10.1166/jolpe.2014.1321

Pickett MD, Medeiros-Ribeiro G, Williams RS (2013) A scalable neuristor built with Mott memristors. Nat Mater 12(2):114–117. https://doi.org/10.1038/nmat3510

Han J-W, Meyyappan M (2018) Leaky integrate-and-fire biristor neuron. IEEE Electron Device Lett 39(9):1457–1460. https://doi.org/10.1109/LED.2018.2856092

Kim W-K, Bidenko P, Kim J, Sim J, Han J-K, Kim S, Geum D-M, Kim S, Choi Y-K (2021) Vertical InGaAs Biristor for Sub-1 V operation. IEEE Electron Device Lett 42(5):681–683. https://doi.org/10.1109/LED.2021.3070334

Barraud S, Ezzadeen M, Bosch D, Dubreuil T, Castellani N, Meli V, Hartmann JM, Mouhdach M, Previtali B, Giraud B, Noël JP, Molas G, Portal JM, Nowak E, Andrieu F (2020) 3D RRAMs with gate-all-around stacked nanosheet transistors for in-memory-computing. IEEE Int Electron Devices Meeting (IEDM). https://doi.org/10.1109/IEDM13553.2020.9371982

Moon K, Lim S, Park J, Sung C, Oh S, Woo J, Lee J, Hwang H (2019) RRAM-based synapse devices for neuromorphic systems. Faraday Discuss 213:421–451. https://doi.org/10.1039/C8FD00127H

Boybat I, Gallo ML, Nandakumar SR, Moraitis T, Parnell T, Tuma T, Rajendran B, Leblebici Y, Sebastian A, Eleftheriou E (2018) Neuromorphic computing with multi-memristive synapses. Nature Commun 9(1):2514. https://doi.org/10.1038/s41467-018-04933-y

Dutta S, Kumar V, Shukla A, Mohapatra NR, Ganguly U (2017) Leaky integrate and fire neuron by charge-discharge dynamics in floating-body MOSFET. Sci Rep 7(1):8257. https://doi.org/10.1038/s41598-017-07418-y

Kamal N, Singh J (2021) A highly scalable junctionless FET Leaky integrate-and-fire neuron for spiking neural networks. IEEE Trans Electron Devices 68(4):1633–1638. https://doi.org/10.1109/TED.2021.3061036

Han J-K, Yu J-M, Choi Y-K (2022) A junctionless single transistor neuron with vertically stacked multiple nanowires for highly scalable neuromorphic hardware. IEEE Trans Electron Devices 69(6):3142–3146. https://doi.org/10.1109/TED.2022.3167622

Chatterjee D, Kottantharavil A (2019) A CMOS compatible bulk FinFET based ultra-low energy leaky integrate and fire neuron for spiking networks. IEEE Electron Device Lett 40(8):1301–1304. https://doi.org/10.1109/LED.2019.2924259

Kamal AK, Singh J (2020) Simulation-based ultralow energy and high-speed LIF neuron using silicon bipolar impact ionization MOSFET for spiking neural networks. IEEE Trans Electron Devices 67(6):2600–2606. https://doi.org/10.1109/TED.2020.2985076

Wang Z, Crafton B, Gomez J, Xu R, Luo A, Krivokapic Z, Martin L, Datta S, Raychowdhury A, Khan AI (2018) Experimental demonstration of ferroelectric spiking neurons for unsupervised clustering. IEEE Int Electron Devices Meeting (IEDM). https://doi.org/10.1109/IEDM.2018.8614586

Han J-K, Seo M, Kim W-K, Kim M-S, Kim S-Y, Kim M-S, Yun GJ, Lee GB, Yu J-M, Choi YK (2020) Mimicry of excitatory and inhibitory artificial neuron with leaky integrate-and-fire function by a single MOSFET. IEEE Electron Device Lett 41(2):208–211. https://doi.org/10.1109/LED.2019.2958623

Khanday MA, Bashir F, Khanday FA (2022) Single germanium MOSFET-based low energy and controllable leaky integrate-and-fire neuron for spiking neural networks. IEEE Transactions on Electron Devices 69(8):4265–4270. https://doi.org/10.1109/TED.2022.3186274

Atlas TCAD device simulator, Silvaco TCAD software (2017)

Eshraghian JK, Ward M, Neftci E, Wang X, Lenz G, Dwivedi G, Bennamoun M, Jeong DS, Lu WD (2021) Training spiking neural networks using Lessons from Deep Learning. arXiv preprint arXiv:2109.12894

Author information

Authors and Affiliations

Contributions

MAK: Conceptualization, Methodology, Software, Investigation, Writing- Original draft preparation. FAK: Supervision, Conceptualization, Writing- Original draft preparation, Reviewing and Editing. FB: Software, Writing-Original draft preparation, Reviewing and Editing.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Khanday, M.A., Khanday, F.A. & Bashir, F. Single SiGe Transistor Based Energy-Efficient Leaky Integrate-and-Fire Neuron for Neuromorphic Computing. Neural Process Lett 55, 6997–7007 (2023). https://doi.org/10.1007/s11063-023-11245-w

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11063-023-11245-w