Abstract

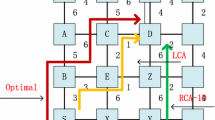

Multiple applications of different criticality are increasingly being executed on the same System-on-Chip (SoC) platform to reduce resource consumption. Communication resources like the Network-on-Chip (NoC) on such platforms can be shared by such applications. Performance can be improved if the NoC is able to adapt at runtime to the requirements of different applications. An important challenge here is guaranteeing Quality of Service (QoS) for critical applications while improving overall performance of critical and non-critical applications. In this paper, we address this challenge by proposing a multi-layered hierarchical NoC which utilizes an adaptive routing algorithm. The proposed routing algorithm determines nodes connecting higher layers at runtime which have a shorter hop count to the destination nodes. Depending on the criticality of the applications, the packets are forwarded on shorter or longer hop paths. An adaptive congestion avoidance feature is integrated. Without congestion awareness, the proposed algorithm which utilizes multiple layers has upto 38% decrease in latency and with congestion awareness has upto 56% decrease in latency compared to the popular XY routing. When comparing algorithms which use different layers, the algorithm with congestion awareness has upto 29% decrease in latency and upto 16% increase in throughput.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Burns, A., Davis, R.I.: A survey of research into mixed criticality systems. ACM Comput. Surv. 50, 6 (2017). Article 82 (January 2018), 37 pages

Benini, L., Micheli, G.D.: Networks on chips: a new SOC paradigm. Computer 35, 70–78 (2002)

Lankes, A., Wild, T., Herkersdorf, A.: Hierarchical NoCs for optimized access to shared memory and IO resources. In: 2009 12th Euromicro Conference on Digital System Design, Architectures, Methods and Tools, Patras, Greece, pp. 255–262 (2009)

Hollis, S.J., Jackson, C.: Skip the analysis: self-optimising networks-on-chip (Invited Paper). In: 2010 International Symposium on Electronic System Design, Bhubaneswar, India, pp. 14–19 (2010)

Hollis, S.J., Jackson, C., Bogdan, P., Marculescu, R.: Exploiting emergence in on-chip interconnects. IEEE Trans. Comput. 63(3), 570–582 (2014). https://doi.org/10.1109/TC.2012.273

Tobuschat, S., Ernst, R.: Providing throughput guarantees in mixed-criticality networks-on-chip. In: 2017 30th IEEE International System-on-Chip Conference (SOCC), Munich, pp. 292–297 (2017)

Heisswolf, J., Bischof, S., Rückauer, M., Becker, J.: Efficient memory access in 2D Mesh NoC architectures using high bandwidth routers. In: 2013 26th Symposium on Integrated Circuits and Systems Design (SBCCI), Curitiba, Brazil, pp. 1–6 (2013)

Avramenko, S., et al.: QoSinNoC: analysis of QoS-aware NoC architectures for mixed-criticality applications. In: 2018 IEEE 21st International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Budapest, pp. 67–72 (2018)

Maleki, A., Ahmadian, H., Obermaisser, R.: Fault-tolerant and energy-efficient communication in mixed-criticality networks-on-chips. In: 2018 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Tallinn, pp. 1–7 (2018)

Dridi, M., Rubini, S., Lallali, M., Flórez, M.J.S., Singhoff, F., Diguet, J.-P.: Design and Multi-Abstraction-Level Evaluation of a NoC Router for Mixed-Criticality Real-Time Systems. J. Emerg. Technol. Comput. Syst. 15, 1 (2019). Article 2 (February 2019), 37 pages

Acknowledgements

This work was funded by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) - project number 146371743 - TRR 89: Invasive Computing.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Switzerland AG

About this paper

Cite this paper

Anantharajaiah, N., Zhang, Z., Becker, J. (2021). Multi-layered NoCs with Adaptive Routing for Mixed Criticality Systems. In: Derrien, S., Hannig, F., Diniz, P.C., Chillet, D. (eds) Applied Reconfigurable Computing. Architectures, Tools, and Applications. ARC 2021. Lecture Notes in Computer Science(), vol 12700. Springer, Cham. https://doi.org/10.1007/978-3-030-79025-7_9

Download citation

DOI: https://doi.org/10.1007/978-3-030-79025-7_9

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-79024-0

Online ISBN: 978-3-030-79025-7

eBook Packages: Computer ScienceComputer Science (R0)